FPGA

首頁 FPGA

品質的堅持

Hyper-Q 和 Alink

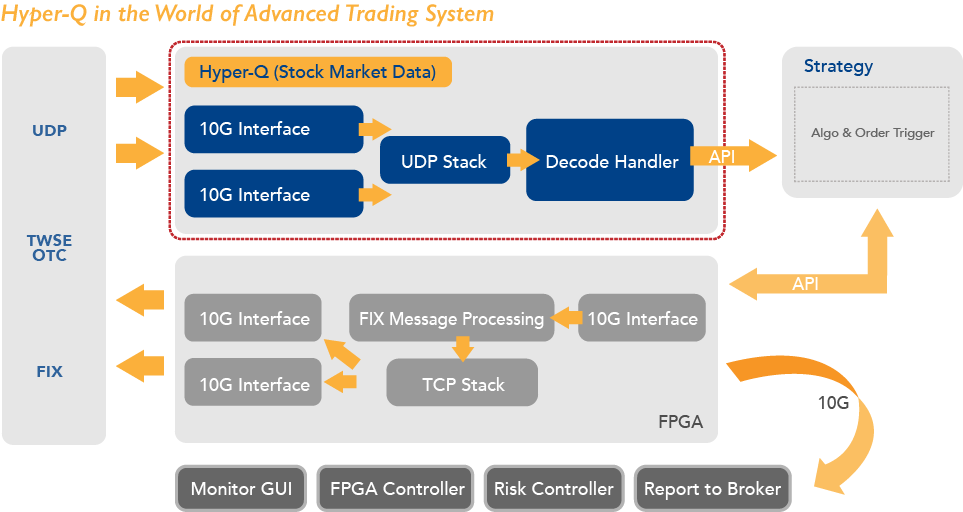

Hyper-Q和Alink 是目前唯一支援台灣證交所的FPGA產品、無論在行情或FIX交易,都已上線實戰多時,是成熟產品。我們研發團隊皆來自知名晶片設計公司的成員所組成,這是台灣第一家結合FPGA和金融交易的成功案例。

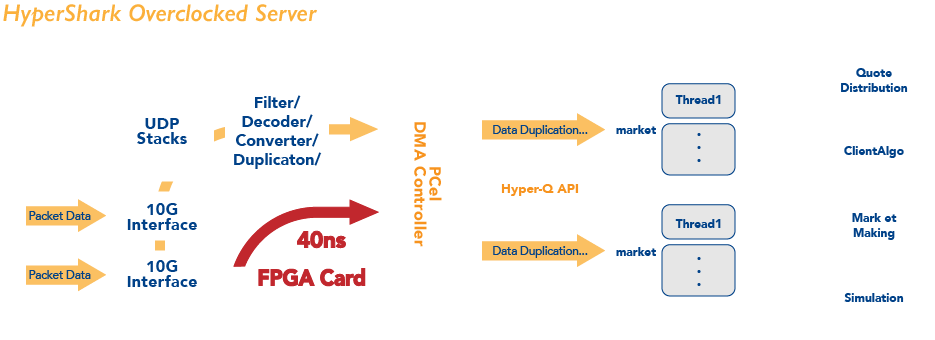

Hyper-Q是台灣證券行情主機,其中即是以FPGA處理行情封包,在幾乎不耗Latency的狀況下(僅PCIE處理時間)將處理完的行情資料結構,透過API讓使用者容易銜接。

Alink是結合行情與下單的Tick to Trade solution,下單所耗掉的Latency低於1μ,使用者具機密性的程式碼可放於user space,FPGA平台皆提供API串接,且與user space的溝通一律是bypass kernel。

Hyper-Q

系統特色及技術指標

HYPER-Q是目前在地首創首套FPGA的台股報價產品,

即時接收TWSE行情封包,

並以快於軟體速度10倍以上的速度DMA到主記憶體,

行情資料會針對每個市場複製多份,

使用者可針對core數決定如何訂閱行情資料,

透過API,使用者可快速上手此絕佳方案。

應用在金融交易的優勢

Hyper-Q Architecture

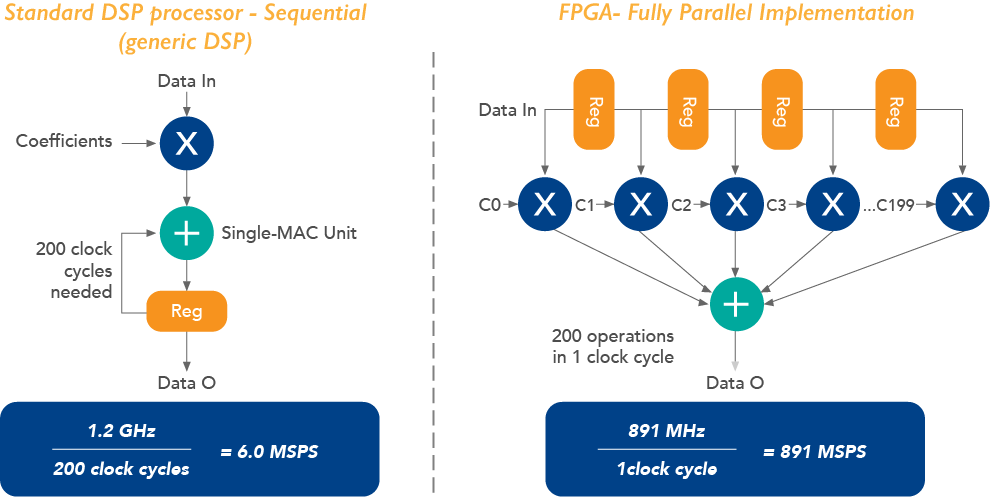

大量的平行化處理

平行計算是一種計算類型,透過平行計算可同時處理多個計算或或者多個執行程序。 一般複雜的工作可以將其切分為較小的工作項目,使這些小的工作項目透過平行計算同時完成。 平行計算有幾種不同形式:bit-level,指令集層級,資料 和 task的平行化。 長期以來,平行計算已被用於高性能計算中。 FPGA在這部分扮演了異常出色的且是可擴展解決方案,這是FPGA的優勢之一。

低延遲且免於抖動

FPGA可以提供精準所消耗的時間,這意味著FPGA沒有抖動的問題且它反應時間是精準可預期的。而軟體這部分恰恰 與FPGA解決方案相反,在作業系統上所運行中的程序可能會被CPU調度程序或硬體IO所中斷。

這導致處理時間會隨著抖動的問題變得不可預期,這也就是為什麼在作業系統中為何latency會呈現出上下飄移的狀況。

簡化數據以提高效率

透過HYPER-Q ,FPGA會將報價資料做過濾處理,僅會將行情最佳五檔及成交明細透過DMA傳到主記憶體;同時精簡化的報價資料結構,可使使用者視CPU的結構更有效率的處理報價資料。

彈性設計

FPGA會將報價資料轉換成米特設計的quote 資料結構,資料結構不超過64 bytes,此設計是為了讓CPU處理更有效率。

透過Hyper-Q API,使用者可以有各種應用,如報價轉送、程式交易、自營交易以及造市。每單一市場Hyper-Q皆會複製多份,使用者可針對CPU 核心數決定多工處理。

行業與應用

HYPER-Q行情解決方案

HyperShark針對台灣證交所所設計的行情解決方案-HYPER-Q,此產品從資料過濾、數據解碼,及DMA到主記憶體的設計都是由FPGA完成,透過精簡化行情資料結構,使user space 可以取得更有效率、低延遲的優勢。

為什麼HYPER-Q可以克服挑戰,實現如此出色的性能

語言

我們在FPGA上使用純Verilog編程,Verilog是低階的硬體語言,Verilog是目前效率最好的選項

測試

我們為FPGA解決方案構建了一套非常獨特的測試環境,可達到精確地測量每個數據包的確切延遲時間

人才

我們從IC設計公司招募了專業人才,其中大多數人了解金融市場的特點並知道如何解決瓶頸

我們知道如何在軟體和硬體之間取得最佳方案,依我們多年的經驗,並非所有系統都納入硬體編成才是好的方案

一來硬體開發時間長,二來成本高,所以知道將FPGA的開發放在最有效率的地方變得非常重要

Alink

FPGA Tick to Trade Solution

Alink系統是由兩個 FPGA 子系統所組成: Hyper-Q和 Alink-O。

Hyper-Q負責解析證交所UDP封包,過濾解碼後組成精簡的quote structure在傳到主記憶體供軟體使用,這部份可參考Hyper-Q的詳細介紹。

Alink-O主要是透過FPGA處理下單,透過Alink API將委託單送出後,FPGA內會處理包含風控、FIX格式轉換後將委託單送交易所,除此之外,委託回報或drop copy皆包含在FPGA的實作中。

Alink-O也可以說是一個 FIX Gateway加速器。

系統特色及技術指標

Latency in Alink System

低延遲

Verilog 是低階的程式語言,在FPGA可使用的程式語言中,Verilog相較下可以取得非常好的優勢,Alink System 就是完全以Verilog所撰寫。

平行處理

FPGA接收資料同時也在處理資料,平行處理網路封包,加速等待封包時間。行情資料DMA到主記憶體時,每個市場複製三份資料,加速策略程式處理行情資訊。

FPGA處理FIX格式及轉換,且實作FIX protocol與交易所FIX Gateway串接,整體處理速度在100M的環境下僅需300nanos。

每筆買單和賣單皆會檢核額度和庫存部位。

link系統從收到行情到下單,內部處理時間僅需1.1μs,不涵蓋策略時間,如以同架構軟體所耗的時間縮短至少10 to 25μs。

產業應用與分享

Functions in Alink System

彈性設計

‧使用者介面可以輸入FPGA控制參數,如FIX Session管理、風控參數值、交易相關參數等

‧Alink系統支援TSE和OTC兩個市場,目前台灣市場唯一FPGA支援下單產品

‧Alink系統支援股票及ETF和權證

支援券商端需求

‧可另提供drop copy資料

‧可另提供批次上傳委託資料

‧透過使用者介面,使用者可透明取得風控值及即時停單功能

系統穩定考量

‧使用者可遠端監控本系統執行狀態,確保資料或相關維護程式的正常性

‧即時FIX線路狀態更新

‧即時更新風控值,使用者可以從外部透明了解風控關資訊

‧提供外部緊急停單控制項

經驗分享

FPGA在金融領域研發難度和困境

開發成本高

實驗室、模擬產品及硬體設備,如再加上軟硬體研發費用,成本是純軟研發數倍以上。

人才整合難

需跨金融與FPGA兩個領域,要提高FPGA專案的成功率務必結合軟硬體專才合作、測試、驗證,但撰寫Verilog和軟韌體好手難尋

產品進程遠

相較於軟體,同樣的功能,Verilog有可能需要10倍程式量,Alink是純Verilog所開發的FPGA 產品,產品要成熟穩定,程式量和難度更高。

研發難度高

測試模擬程式需要涵蓋Verilog模擬器、以及軟體驗證測試。載體的相容性測試也需要考量,驗證上需檢核的問題類型相對複雜。

Alink 的現況與未來

產品已真實上線,具實戰經驗且是成熟的產品

完整的模擬交易所環境進行模擬

已經歷市場各式情境,最穩定的的FPGA solution

-

2019-05

Alink System

-

2020-03

Hyper-Q Stock

-

Coming Soon

Hyper-Q Futures

-

Coming Soon

Extreme-O Futures

-

服務介紹

首頁 超頻伺服器 FPGA高速交換機 -

支援

常見問答 保固資訊 下載專區 合作夥伴 -

關於米特

公司介紹 認證專利 新知分享 徵才資訊 -

聯絡我們

+8862 2396 9789 100台北市中正區仁愛路二段2號7樓 service@hypersharktech.com

-

SERVICE

HOME OVERCLOCKED FPGASWITCH -

SUPPORT

FAQ warranty downloads partner -

company

about certification NEWS career -

contact

+8862 2396 9789 7TH FLOOR, NO. 2, SECTION 2, REN'AI ROAD,ZHONGZHENG DISTRICT, TAIPEI CITY service@hypersharktech.com

Copyright © 2020 HyperShark Technologies Corp. All Rights Reserved.